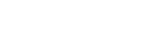

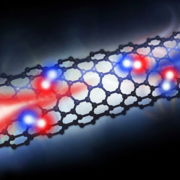

近日,中科院高鸿钧、鲍丽宏、马里兰大学欧阳敏等报道基于InSe/hBN/多层石墨烯van der Waals异质结界面,制备达到纳秒的超高速可编程/擦写器件,消光比达到1010。复旦大学周鹏、陈时友等报道在MoS2/hBN/多层石墨烯 van der Waals异质结实现了20 纳秒的超快写入/擦除速度。在两项报道中,都实现了20纳秒写入/擦除速度,同时保留时间能够达到10年。器件通过原子层厚度二维材料层-层组装实现,实现了异质结、隧穿完美结合,通过异质结将不同材料中能级不同的电子结合,因此载流子发生限域;隧穿作为一种电子穿越势垒的量子力学效应,对电场的强度非常敏感。麦吉尔大学Thomas Szkopek对该工作进行总结,对其意义进行评述和展望。

参考文献

Szkopek, T. Ultra-fast non-volatile memory. Nat. Nanotechnol. (2021).

DOI: 10.1038/s41565-021-00932-1

https://www.nature.com/articles/s41565-021-00932-1

Wu, L., Wang, A., Shi, J. et al. Atomically sharp interface enabled ultrahigh-speed non-volatile memory devices. Nat. Nanotechnol. (2021).

DOI: 10.1038/s41565-021-00904-5

https://www.nature.com/articles/s41565-021-00904-5

Liu, L., Liu, C., Jiang, L. et al. Ultrafast non-volatile flash memory based on van der Waals heterostructures. Nat. Nanotechnol. (2021).

DOI: 10.1038/s41565-021-00921-4