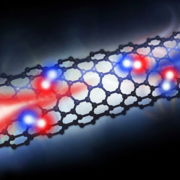

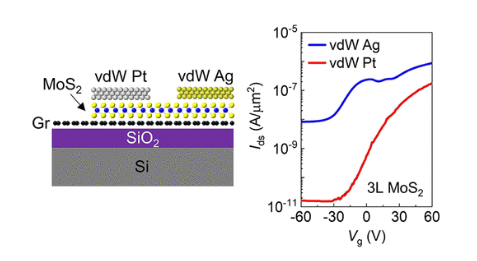

垂直晶体管为超大规模晶体管的发展提供了希望。然而,它们的通断比受到关断状态下强大的源漏隧道电流的限制,特别是对于沟道长度小于5 nm的垂直器件。

在这里,湖南大学Yuan Liu报道了一种通过范德华金属接触设计势垒高度来抑制关态隧道电流的方法。

文章要点

1)通过在MoS2垂直晶体管上叠层铂电极,由于功函数差较大,观察到高肖特基势垒,从而抑制了直接隧穿电流。同时,这种“低能量”层压工艺确保了优化的金属/MoS2界面,使界面状态和缺陷降至最低。

2)沟道长度分别为5 nm和2 nm的垂直晶体管通断比最高,分别为5×105和104。因此,研究工作不仅推动了垂直晶体管的通断比极限,而且为减小超大规模器件的短沟效应提供了一般规律。

参考文献

Likuan Ma, et al, Realizing On/Off Ratios over >104 for Sub‑2 nm Vertical Transistors, Nano Lett., 2023

DOI: 10.1021/acs.nanolett.3c02518

https://doi.org/10.1021/acs.nanolett.3c02518